- 您现在的位置:买卖IC网 > Sheet目录1214 > EVAL-ADE7880EBZ (Analog Devices Inc)BOARD EVAL FOR ADE7880

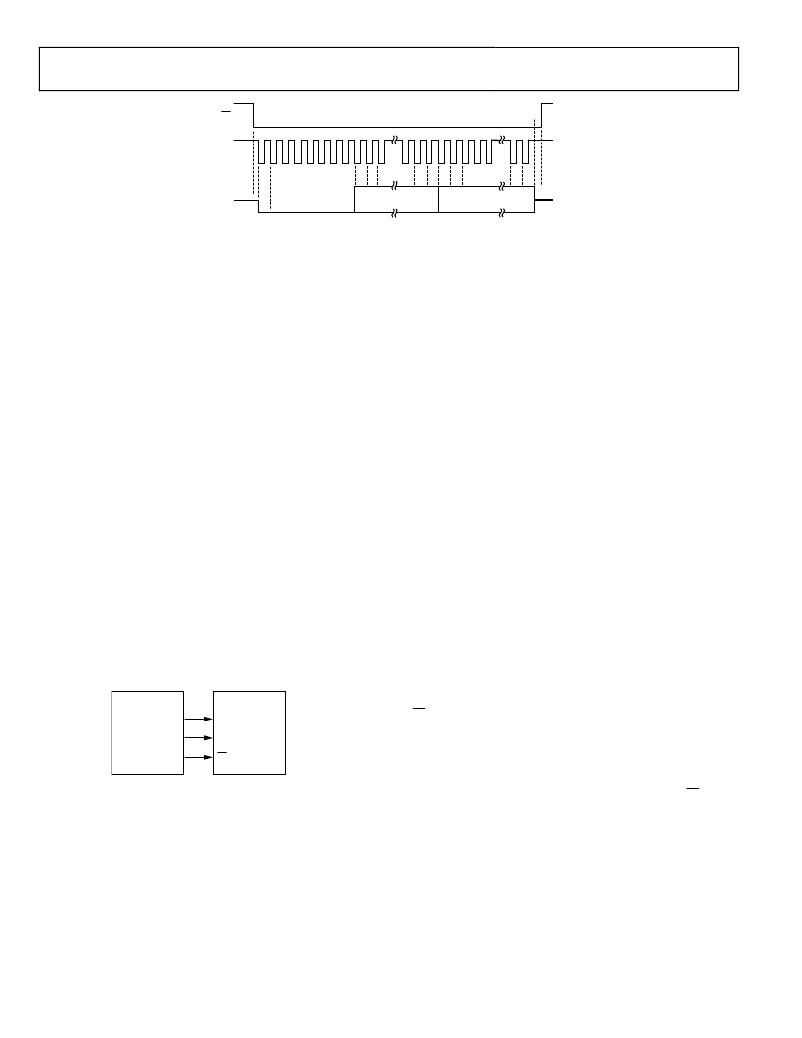

�� �

�

�

�ADE7880�

�SS�

�SCLK�

�Data� Sheet�

�15� 14�

�1� 0� 31� 30�

�1� 0�

�MOSI�

�0� 0� 0� 0� 0� 0� 0� 0�

�REGISTER� ADDRESS�

�REGISTER� VALUE�

�Figure� 106.� SPI� Write� Operation� of� a� 32-Bit� Register�

�HSDC� Interface�

�The� high� speed� data� capture� (HSDC)� interface� is� disabled� after�

�default.� It� can� be� used� only� if� the� ADE7880� is� configured� with� an�

�I� 2� C� interface.� The� SPI� interface� of� ADE7880� cannot� be� used� at�

�the� same� time� with� HSDC.�

�Bit� 6� (HSDCEN)� in� the� CONFIG� register� activates� HSDC� when�

�set� to� 1.� If� Bit� HSDCEN� is� cleared� to� 0,� the� default� value,� the�

�HSDC� interface� is� disabled.� Setting� Bit� HSDCEN� to� 1� when� SPI�

�is� in� use� does� not� have� any� effect.� HSDC� is� an� interface� for�

�sending� to� an� external� device� (usually� a� microprocessor� or� a�

�DSP)� up� to� sixteen� 32-bit� words.� The� words� represent� the�

�instantaneous� values� of� the� phase� currents� and� voltages,� neutral�

�current,� and� active,� reactive,� and� apparent� powers.� The� registers�

�being� transmitted� include� IAWV,� VAWV,� IBWV,� VBWV,� ICWV,�

�VCWV,� AVA,� INWV,� BVA,� CVA,� AWATT,� BWATT,� CWATT,�

�AFVAR,� BFVAR,� and� CFVAR.� All� are� 24-bit� registers� that� are�

�sign� extended� to� 32-bits� (see� Figure� 44� for� details).�

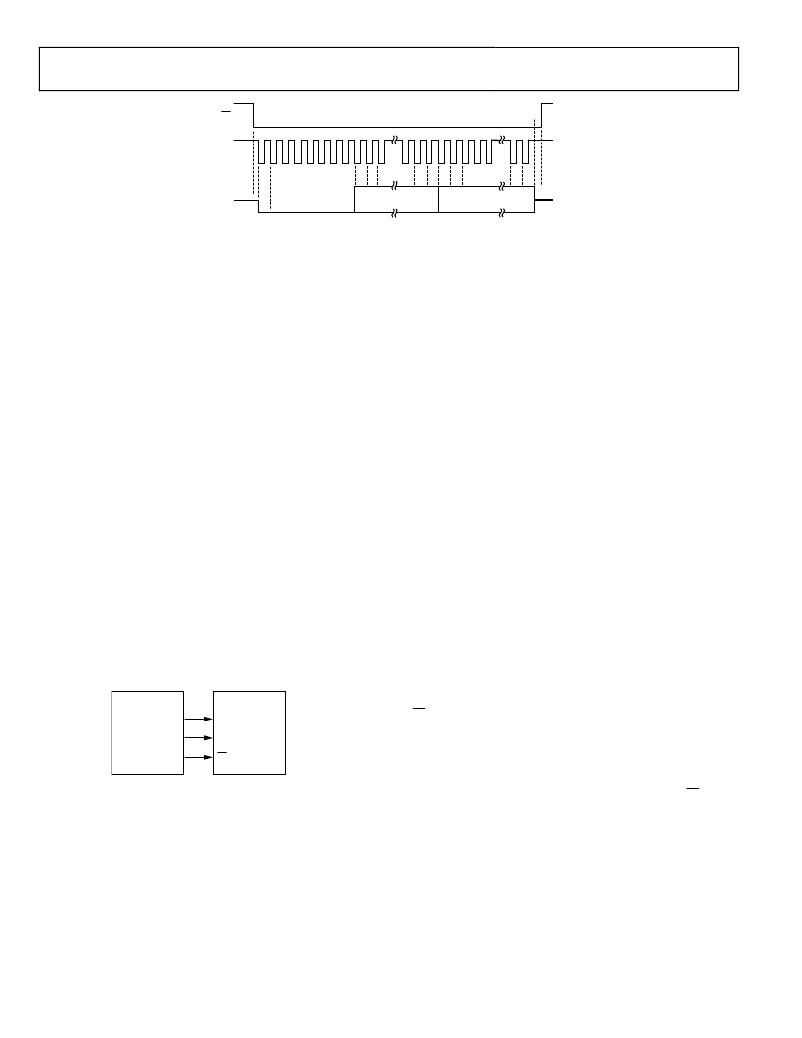

�HSDC� can� be� interfaced� with� SPI� or� similar� interfaces.� HSDC� is�

�always� a� master� of� the� communication� and� consists� of� three�

�pins:� HSA,� HSD,� and� HSCLK.� HSA� represents� the� select� signal.�

�It� stays� active� low� or� high� when� a� word� is� transmitted� and� it� is�

�usually� connected� to� the� select� pin� of� the� slave.� HSD� sends� data�

�to� the� slave� and� it� is� usually� connected� to� the� data� input� pin� of�

�the� slave.� HSCLK� is� the� serial� clock� line� that� is� generated� by� the�

�ADE7880� and� it� is� usually� connected� to� the� serial� clock� input� of�

�the� slave.� Figure� 107� shows� the� connections� between� the�

�ADE7880� HSDC� and� slave� devices� containing� an� SPI� interface.�

�is� 1,� the� clock� frequency� is� 4� MHz.� A� bit� of� data� is� transmitted�

�for� every� HSCLK� high-to-low� transition.� The� slave� device� that�

�receives� data� from� HSDC� samples� the� HSD� line� on� the� low-to-�

�high� transition� of� HSCLK.�

�The� words� can� be� transmitted� as� 32-bit� packages� or� as� 8-bit�

�packages.� When� Bit� 1� (HSIZE)� in� the� HSDC_CFG� register� is� 0� (the�

�default� value),� the� words� are� transmitted� as� 32-bit� packages.� When�

�Bit� HSIZE� is� 1,� the� registers� are� transmitted� as� 8-bit� packages.� The�

�HSDC� interface� transmits� the� words� MSB� first.�

�Bit� 2� (HGAP)� introduces� a� gap� of� seven� HSCLK� cycles� between�

�packages� when� Bit� 2� (HGAP)� is� set� to� 1.� When� Bit� HGAP� is�

�cleared� to� 0� (the� default� value),� no� gap� is� introduced� between�

�packages� and� the� communication� time� is� shortest.� In� this� case,�

�HSIZE� does� not� have� any� influence� on� the� communication� and�

�a� data� bit� is� placed� on� the� HSD� line� with� every� HSCLK� high-to-�

�low� transition.�

�Bits[4:3]� (HXFER[1:0])� decide� how� many� words� are� transmitted.�

�When� HXFER[1:0]� is� 00,� the� default� value,� then� all� 16� words� are�

�transmitted.� When� HXFER[1:0]� is� 01,� only� the� words� representing�

�the� instantaneous� values� of� phase� and� neutral� currents� and� phase�

�voltages� are� transmitted� in� the� following� order:� IAWV,� VAWV,�

�IBWV,� VBWV,� ICWV,� VCWV,� and� one� 32-bit� word� that� is� always�

�equal� to� INWV.� When� HXFER[1:0]� is� 10,� only� the� instantaneous�

�values� of� phase� powers� are� transmitted� in� the� following� order:�

�AVA,� BVA,� CVA,� AWATT,� BWATT,� CWATT,� AFVAR,� BFVAR,�

�and� CFVAR.� The� value,� 11,� for� HXFER[1:0]� is� reserved� and�

�writing� it� is� equivalent� to� writing� 00,� the� default� value.�

�ADE7880�

�HSD�

�HSCLK�

�HSA�

�SPI� DEVICE�

�MISO�

�SCK�

�SS�

�Bi� t� 5� (HSAPOL)� determines� the� polarity� of� HSA� function� of� the�

�SS/HSA� pin� during� communication.� When� HSAPOL� is� 0� (the�

�default� value),� HSA� is� active� low� during� the� communication.�

�This� means� that� HSA� stays� high� when� no� communication� is� in�

�progress.� When� a� communication� is� executed,� HSA� is� low� when�

�Figure� 107.� Connecting� the� ADE7880� HSDC� with� an� SPI�

�The� HSDC� communication� is� managed� by� the� HSDC_CFG�

�register� (see� Table� 52).� It� is� recommended� to� set� the� HSDC_CFG�

�register� to� the� desired� value� before� enabling� the� port� using� Bit� 6�

�(HSDCEN)� in� the� CONFIG� register.� In� this� way,� the� state� of�

�various� pins� belonging� to� the� HSDC� port� do� not� take� levels� incon-�

�sistent� with� the� desired� HSDC� behavior.� After� a� hardware� reset�

�or� after� power-up,� the� MISO/HSD� and� SS/HSA� pins� are� set� high.�

�Bit� 0� (HCLK)� in� the� HSDC_CFG� register� determines� the� serial�

�the� 32-bit� or� 8-bit� packages� are� transferred,� and� it� is� high� during�

�the� gaps.� When� HSAPOL� is� 1,� the� HSA� function� of� the� SS/HSA�

�pin� is� active� high� during� the� communication.� This� means� that�

�HSA� stays� low� when� no� communication� is� in� progress.� When� a�

�communication� is� executed,� HSA� is� high� when� the� 32-bit� or�

�8-bit� packages� are� transferred,� and� it� is� low� during� the� gaps.�

�Bits[7:6]� of� the� HSDC_CFG� register� are� reserved.� Any� value�

�written� into� these� bits� does� not� have� any� consequence� on� HSDC�

�behavior.�

�clock� frequency� of� the� HSDC� communication.� When� HCLK� is�

�0� (the� default� value),� the� clock� frequency� is� 8� MHz.� When� HCLK�

�Rev.� A� |� Page� 78� of� 104�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-ADE7953EBZ

BOARD EVAL FOR ADE7953

EVAL-ADF4002EBZ1

BOARD EVAL FOR ADF4002

EVAL-ADG788EBZ

BOARD EVALUATION FOR ADG788

EVAL-ADM1021AEB

BOARD EVAL FOR ADM1021

EVAL-ADM1023EB

BOARD EVAL FOR ADM1023

EVAL-ADM1031EB

BOARD EVAL FOR ADM1031

EVAL-ADM1062TQEBZ

BOARD EVALUATION FOR ADM1062TQ

EVAL-ADM1075CEBZ

BOARD EVAL FOR ADM1075

相关代理商/技术参数

EVAL-ADE7880EBZ

制造商:Analog Devices 功能描述:ADE7880, ENERGY METER, 3 PH, SPI, I2C, E

EVAL-ADE7913EBZ

制造商:AD 制造商全称:Analog Devices 功能描述:3-Channel, Isolated, Sigma-Delta ADC with SPI

EVAL-ADE7953EBZ

功能描述:BOARD EVAL FOR ADE7953 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-ADF4001EBZ2

制造商:Analog Devices 功能描述:Evaluation Board For Pll Frequency Synthesizer 制造商:Analog Devices 功能描述:ADF4001 PLL SYNTHESIZER EVAL BOARD

EVAL-ADF4002EB1

制造商:Analog Devices 功能描述:EVAL BOARD - Bulk

EVAL-ADF4002EBZ1

功能描述:BOARD EVAL FOR ADF4002 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板

EVAL-ADF4007EBZ1

功能描述:BOARD EVALUATION FOR ADF4007EB1 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-ADF4106EB1

制造商:Analog Devices 功能描述:PLL, Frequency Synthesizer